# 上位ビットから変換するオフセット二進数に対応した SC 循環型 D/A 変換器

中原 広裕 a)·松本 寛樹 b)

# Switched-Capacitor Cyclic D/A Converter from Most Significant Bit of Offset Binary Number

Kousuke NAKAHARA, Hiroki MATSUMOTO

#### Abstract

Switched-capacitor cyclic digital-to-analog converter from most significant bit of offset binary number is presented. The operation is also simulated using circuit simulator SIMetrix. Resolution of 6 bit is confirmed on the proposal converter.

Keywords: Switched-capacitor, Offset binary, Cyclic D/A converter

#### 1. 序論

近年では、マイクロコンピュータやメモリに代表される LSI 技術の発展に支えられ、生活のさまざまな部分にまでデジタル化が進んでおり、日常生活の中になくてはならないものにまでなっている。このデジタルデータを扱ううえで A/D、D/A 変換もまた重要なものであり、より良い物が求められている。身近にある物理量はアナログ量であるが、アナログ量のままでデータを扱うとデータ量は膨大になるため、デジタルへと変換したほうが効率が良くなることが大いにある。そこで、アナログ量をデジタルへと変換させるために A/D 変換器、デジタルのままでは人間が直接認識できないので、再びアナログ量へと戻すために D/A 変換器が必要となる。A/D、D/A変換でも雑音や誤差が乗る為その影響をできるだけ最小限にし、エネルギーの消費も抑えるような低価格、高精度、高速の物が理想である。

本研究ではスイッチトキャパシタ回路を用いて回路の高速化を図り、SIMetrix回路シミュレーターを用いて回路動作の確認を行う。

## 2. 基礎理論

#### 2 .1 SC(Switched Capacitor)回路

SC 回路とは、SwitchedCapacitor 回路の略で、回路には通常、抵抗、コイルといった素子を用いるが、SC 回路では基本的にこれらの素子を使わずにスイッチとコンデンサのみで回路を構成できる。そのため、IC 化も可能であるし、抵抗を使用しないので消費電力の面でも優れているので、将来期待されている。SC 回路の回路動作はスイッチの切り替えによって電荷を転送し回路を動作させる。

- a) 電気電子工学科学部生

- b) 電気電子工学科准教授

動作はスイッチの切り替えによって電荷を転送し回路を動作させる。

#### 2.1 オフセット二進数

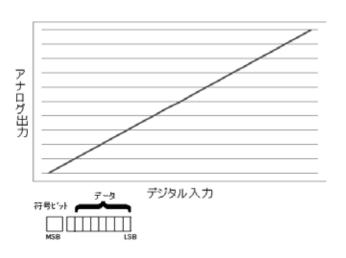

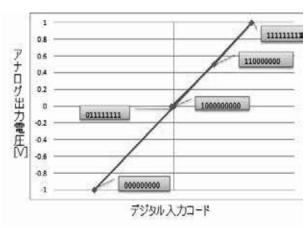

オフセットとは、あるデータの位置を、基準点からの 差(距離)で表した値のこと。(Offset)は、英語で(差 引き計算する)という意味で、そこから転じて、必要な データの位置を基準点からの差(距離)で表した値である。二進数とは、 $0 \ge 1$  の二種類の数字だけで表したものである。二進数の各桁にもそれぞれ重みがあり、一桁 左に書かれた数字は、一桁右の数字よりも二倍の重みをもっている。二進数の基数は、2です。よって、二進数の位置を基準点からの差(距離)で表した値のことである。図1 より符号ビット(MSB)が0 の場合は-1 を足して(MSB)が1 の場合は0 を足す。

図1:オフセット2進数の出力特性

#### 3. 提案回路の説明

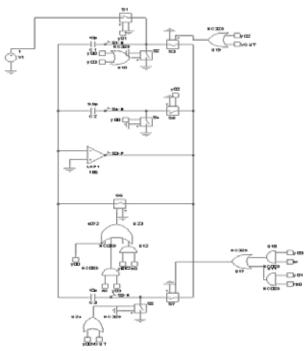

図2の回路は、シフトレジスタを用いて上位ビットからDA変換してVoに出力する回路である。

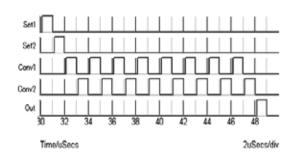

この回路のスイッチ表を表 1 に示す。この回路は、Set  $\phi_1$ 、  $\phi_2$  そして、 $Conv \phi_1$ 、  $\phi_2$  を 8 回繰り返して Out で出力する。  $b_0$  は符号ビットである。

図 2. 上位ビットから変換するオフセット二進数 に対応した SC 循環型 DA 変換器

| に対応したの相塚空 DA 友授品 |            |     |    |    |     |     |      |     |    |  |

|------------------|------------|-----|----|----|-----|-----|------|-----|----|--|

| MODE             | CLOCK      | \$1 | SZ | S3 | \$4 | \$5 | S6   | \$7 | S8 |  |

| SET              | R1         | 0   | 1  | 0  | 1   | 0   | 1    | 0   | 1  |  |

|                  | R2         | 1   | 0  | 0  | Û   | 0   | - 60 | ×Ю  | 0  |  |

| CONV             | <b>#</b> 1 | 0   | 0  | 1  | 0   | 1   | 0    | 0   | 0  |  |

|                  | ΰ2         | 0   | 1  | 0  | 0   | 0   | 16   | Ы   | 0  |  |

| OUT              |            | 0   | 0  | 1  | 0   | 0   | 0    | 0   | 1  |  |

表1 スイッチ判定表

図 3: クロックタイミング図

#### 4. 回路動作

Set  $\phi_1$  ですべてのコンデンサが接地されるため電位 差は 0 となる。

Set  $\phi_2$ で  $C_1$ に基準電圧が充電され、また符号ビットが 出力電圧にたされるために符号ビットが O ならば  $C_3$  に Vr が充電される。

$Conv \phi_1$ で  $C_1$  または  $C_2$  の電荷が  $C_1$  と  $C_2$  に分けられる。

$Conv \phi_2 \sigma C_1$ の電荷が0となり、 $C_3$ に電荷が充電される。

Out で C<sub>3</sub>の電圧が Vo に出力される。

#### 5. D/A 変換アルゴリズム

循環型 D/A 変換器はデジタル信号を1ビットずつ等価なアナログ電圧に変換する。MSB からデータ変換を開始する場合は、次式に示される演算をn回繰り返すことによってアナログ電圧 Va が得られる。

$$V(i) = V(i-1) + b_i 2^{-i} V_r$$

$V(0)=(b_0-1)\ V_r$ 、V(n)=Va となる。 上式より、データ変換器の入力と出力は次式で関係づけられる。

$$\begin{aligned} V_a &= \sum_{i=1}^{n-1} b_i 2^{-i} V r + (b_0 - 1) V_r \\ &= (b_0 - 1) V_r + \sum_{i=1}^{n-1} b_i 2^{-i} V r \end{aligned}$$

#### 6. シミュレーション結果

|       | 000000000 | 100000000 | 111111111 | 110000000 | 0111111111 |

|-------|-----------|-----------|-----------|-----------|------------|

| 実験値   | -996.04   | 2.61 uV   | 968.45    | 499.81    | -31.25     |

| 計算値   | -1000     | 0         | 996.09    | 500       | -3.91      |

| 誤差(%) | 0.0003    | 2.61 uV   | 0.0276    | 0.00019   | 0.0273     |

表 2. 実験値と計算値の誤差表

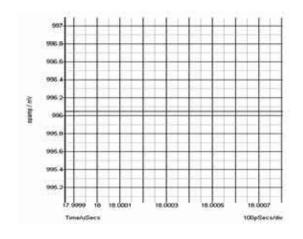

図 4. シミュレーション結果のグラフ

図 5. 9 ビット D/A 変換の出力特性

図4は、入力コード(111111111)の時の出力波形である。表2は、各入力コードの実験値から計算値を引いた誤差表である。

#### 7. 従来回路との比較

提案回路との違いは、CONVERT MODE を 1 セットしか行わず、また n 回繰り返す。それ以外の動作原理は提案回路と同じである。従来回路の誤差電圧については、 $C_1$ =10[pF],  $C_2$ =9.9[pF]とした。そして、最大誤差の大きさを求めたが、入力信号(111111111)のときが最大で9.9[mV]となり、1 LSB の精度により、6 ビットの分解能を持つことができる。

#### 8. 結論

今回はスイッチキャパシタ、オペアンプを用いた高速循環型 D/A 変換器の回路を提案し、動作確認を行った。この提案回路の目的は、入力データの D/A 変換器の時間を短縮することである。オフセット二進数は、序論で述べたように、符号ビット1の時は、0を足して、符号ビット0の時は-1を足しものであった。

今回の測定結果は表2に示した通りになった。 また、これは、図5と表すことができ、オフセット二進 数に対応しているがわかる。

提案回路は、従来の循環型 D/A 変換器と比較して変換 速度を約 1/2 に短縮することができた。

入力コード (000000000)、(1111111111)、(011111111)、(110000000)、(100000000) の時のシミュレーションを行ったが、入力信号 (1111111111) の時、誤差電圧 0.0276[mV]が得られた。この時、15bit の分解能を持つことがわかる。

従来の回路では、6 ビットの分解能を持っているが、 提案回路では、15 ビットの分解能を持っており、高い精 度を持つ D/A 変換器に改善できた。

## 参考文献

- 1) 渡辺健蔵・松本寛樹・藤原一伸著 スイッチトキャパシタ循環型データ変換器 1985

- 2) 藤井 信生: アナログ電子回路の基礎, 昭晃堂, 2004.