### 単一利得増幅器を用いた容量比に鈍感な SC 逐次近似型 D/A 変換器

甲斐 康平 a)·牧 直人 b)·松本 寬樹 c)

# A Switched-Capacitor Successive-Approximation D/A Converter insensitive to Capacitance Ratio using Unity-Gain Buffers.

Kouhei KAI, Naoto MAKI, Hiroki MATSUMOTO

#### **Abstract**

In this paper, we propose a new Switched-Capacitor (SC) successive-approximation Digital-to-Analog Converter (DAC). The converter is insensitive to capacitance mismatch using unity-gain buffers. Circuit operation is evaluated by SIMetrix. On this simulation, 15 bits accuracy has been obtained.

*Keywords*: Unity-Gain Buffer, Swiched-Capacitor, DAC, capacitance mismatch, Successive-Approximation

#### 1. 序論

近年、これまでアナログ信号で行われていた分野が 次々とディジタル信号へと置き換えられている。我々の 日常生活の中でテレビやエアコン、電子レンジなどの家 電製品をはじめ、様々なものにディジタル信号処理技術 が使用されるようになってきた。

ここで、身の回りの物理量は時間的に連続なアナログ信号がほとんどである。従って、アナログ信号をディジタル信号に変換する A/D 変換器、ディジタル信号を処理した後再び元のアナログ信号に戻すための D/A 変換器が必要となる。その技術が、A/D 変換または D/A 変換であり、低価格化、高精度化、高速化などを目指した高い信頼性をもつ A/D 変換器、D/A 変換器の開発が進められている。

今回提案する D/A 変換器は、高精度でかつ安定な特性が実現でき、消費電力を大幅に低減できるスイッチトキャパシタ(SC)回路を用いる。ここで、SC 回路を構成しているキャパシタには、製造時のばらつきや温度変化、経年変化などの原因によって誤差が生じる。それにより、SC 回路で構成する D/A・A/D 変換器において容量不整合が生じて最終的な出力電圧や出力電流に影響する。

また、入力ビットの最上位ビットから 1 ビットずつ変換する逐次近似型であるため、その分変換時間がかかる

- a) 大学院電気電子工学専攻

- b) 工学部電気電子工学科

- c) 工学部准教授

が、ビット数が多くても限られた素子で構成できることによって低価格化の実現、そして、キャパシタの充放電に単一利得増幅器を用いることで、高速化が実現できる。本研究では、容量不整合の影響を小さくし、従来回路の精度をより向上させた単一利得増幅器を用いた容量比に鈍感な SC 逐次近似型 D/A 変換器を提案する。

#### 2. 基本構成

この章では D/A 変換やキャパシタンス不整合時の誤差 について述べる。

#### 2.1 単一利得増幅器

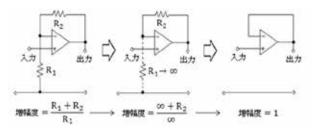

単一利得増幅器としての用途に、ボルテージホロワが使われる。ボルテージホロワとは、増幅度 1の非反転増幅回路のことである。ボルテージホロワの概略を図 2.1に示す。回路で増幅度を1にするためには、 $R_1$ を無限大にする(取り去ってしまう)のが最も簡単な方法である。この場合、 $R_2$ は結果に影響しないため、最終的には出力端子と入力端子を直結した負帰還 100%の単純な回路となる。

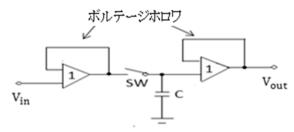

図 2.2 に単一利得増幅器の用途として用いられるボルテージホロワとキャパシタで構成されたサンプルホールド(S/H)回路例を示す。この回路では、フィードバック抵抗を通さないため、キャパシタの充放電時に高速化されるが、単一利得増幅器を用いた場合、キャパシタの節点と接地間に寄生容量が生じるため、出力電圧に影響す

る。動作は、スイッチ SW がオン状態で、出力電圧  $V_{out}$  は入力電圧  $V_{in}$  に等しい。スイッチ SW がオフ状態では入出力間が遮断されるが、コンデンサ C にはスイッチ SW がオフになる直前の入力電圧が保持されたままになっているので、C の電圧が出力電圧  $V_{out}$  となる。

図 2.1 ボルテージホロワの概略図

図 2.2 サンプルホールド(S/H)回路例

#### 2.2 スイッチド・キャパシタ(SC) 回路

スイッチド・キャパシタ(SC)回路は、通常の回路で用いる抵抗やコイルといった素子を使用せず、MOS スイッチとキャパシタおよび演算増幅器または単一利得増幅器から構成され、スイッチの周期的な開閉により電荷の充放電と転送を行って動作させる。また、SC 回路はアナログサンプル値回路であるから、アナログ情報源とディジタル通信・処理装置とのインターフェース部や通信伝送路等に挿入され、フィルタや等化器にも用いられる。その他にも、スイッチを含んでいることから、D/A変換や A/D 変換器、変調器、発振器を構成するのにも用いられる。

SC 回路の大きな特徴は、集積回路として実現した場合、他のアナログ回路に比べて、高精度でかつ安定な特性が実現できること、およびチップ面積と消費電力を大幅に低減できることである。MOS 集積回路は、情報を荷っている物理量が電荷であり、この電荷を比較的長い時間に渡って保持したり、クロック制御により転送することが可能である。さらに、アナログ-ディジタル混在回路の集積化にも適している。しかし、このような利点がある反面、寄生容量を介して信号線に誘導される電源雑音、ディジタル雑音および漏話などの問題点もある。このため、集積回路の設計においては、高性能化、小型化およ

び低消費電力化と共に、雑音の低減が重要な課題となっている。

#### 2.3 D/A 変換

D/A 変換とは、ディジタルからアナログに復元することである。これを実行する再生回路は、基本的にディジタルからアナログに変換する D/A 変換と、波形を整えるための再生フィルタと後置フィルタにより成り立っており、これらを含めて D/A 変換器という。

D/A 変換の過程は、基本的に符号化されたディジタル 入力信号から再生回路を通ってその入力に与えられた 数値に見合うアナログ出力電流または電圧に変換して いくことである。2 進数で表されるシステム内で、その 最大の値を表す桁を最上位ビット(MSB)、最小の値を表 す桁を最下位ビット(LSB)という。

入力信号は量子化された離散的な"0"と"1"からなる周期 T を持つディジタル信号で、自然 2 進コードによる振幅幅一定のパルス列である。次に、周期ごとにアナログのインパルス列へと変換(再生化)していき、振幅値は量子化により不連続である。その後、インパルス列を変換期間中、一定レベルに保ってステップ・パルス列とする(ステップ・パルス化)。ここで、再生フィルタによってアナログによるインパルス列間の空間を満たし、アナログ出力を連続かつスムーズにする。出力信号は連続的なアナログ信号であり、アナログ波形を滑らかにするために、最後に後置フィルタを通すことによって初めて綺麗なアナログ波形が出力される。

#### 2.4 容量不整合

2 つのコンデンサを  $C_1$  と  $C_2$  として、 $C_1$  と  $C_2$ 間の容量 不整合  $\epsilon$  を式(2.1)に示す。

$$\varepsilon = \frac{C_1 - C_2}{Cu} \tag{2.1}$$

ここで、2つのコンデンサの平均容量 Cuを

$$Cu = \frac{C_1 + C_2}{2} \tag{2.2}$$

とおく。それで、

$$\begin{cases} C_1 = Cu\left(1 + \frac{\varepsilon}{2}\right) \\ C_2 = Cu\left(1 - \frac{\varepsilon}{2}\right) \end{cases}$$

(2. 3)

が得られる。

## 3. 単一利得増幅器を用いた容量比に鈍感な SC 逐次型 D/A 変換器

#### 3.1 従来回路

#### 3.1.1 回路構成

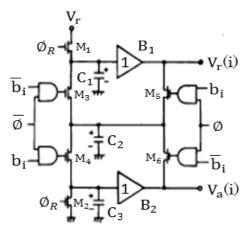

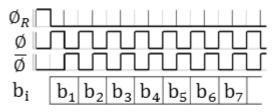

図 3.1 に文献[6]のスイッチドキャパシタ逐次近似型 D/A 変換器を示す。この回路は互いに重なり合わないクロックを用いて動作し、図 3.2 にクロック信号を示す。また、基準電圧を $V_r$ 、入力ビットを $b_i$ 、出力電圧 $V_a$ とし、利得1の単一利得増幅器を用いる。ここで、 $C_1$ と $C_2$ の間、 $C_2$ と $C_3$ の間の容量不整合をそれぞれ $\epsilon_1$ ,  $\epsilon_2$ とする。

図 3.1 スイッチドキャパシタ逐次近似型 D/A 変換器

図 3.2 クロック信号

#### 3.1.2 回路動作

$\emptyset$ クロック:  $b_i=1$  の時、 $C_1$  の電荷は  $C_2$  へ転送される。  $C_3$  の電荷は保持される  $b_i=0$  の時、 $C_3$  の電荷は保持される。  $C_1$  の電荷は保持される

$\overline{\emptyset}$ クロック:  $b_i=1$  の時、 $C_2$ に充電されている  $V_r$ が  $C_3$  と分圧され、それぞれの電荷は $2^{-i}V_r$ となる。  $C_1$  の電荷は保持される。  $b_i=0$  の時、 $C_1$  に 充電されている  $V_r$ が  $C_2$  と分圧され、それぞれの電荷は $2^{-i}V_r$ となる。 $C_3$  の電荷は保持される。

以降、同じようにn回繰り返し、1ビットずつ変換して出力電圧 $V_a$ に出力される。

#### 3.1.3 D/A 変換アルゴリズム

従来回路の D/A 変換において n ビット変換行う場合、基準電圧を $V_r$ 、入力ビットを $b_i$ とすれば、出力電圧 $V_a$ は式(3.1)の D/A 変換アルゴリズムの行列式が得られる。

$$\begin{pmatrix} V_r(i) \\ V_a(i) \end{pmatrix} = \begin{pmatrix} b_i + \frac{\overline{b_i}}{2} & \frac{\overline{b_i}}{2} \\ \frac{b_i}{2} & \overline{b_i} + \frac{b_i}{2} \end{pmatrix} \begin{pmatrix} V_r(i-1) \\ V_a(i-1) \end{pmatrix} \quad (3. 1)$$

また、容量不整合 $\epsilon$ を含む場合のアルゴリズムは式(3.2) で表される。

$$\begin{pmatrix} V_r(i) \\ V_a(i) \end{pmatrix} = \begin{pmatrix} b_i + \overline{b_i} \frac{1 + \varepsilon_1/2}{2} & \overline{b_i} \frac{1 - \varepsilon_1/2}{2} \\ b_i \frac{1 + \varepsilon_2/2}{2} & \overline{b_i} + b_i \frac{1 - \varepsilon_2/2}{2} \end{pmatrix} \begin{pmatrix} V_r(i-1) \\ V_a(i-1) \end{pmatrix}$$

(3. 2)

ここで $\epsilon_1$ と $\epsilon_2$ は次式に定義する。

$$\varepsilon_1 = \frac{C_1 - C_2}{C_{11}}, \varepsilon_2 = \frac{C_2 - C_3}{C_{11}}$$

(3. 3)

#### 3.2 提案回路

#### 3.2.1 回路構成

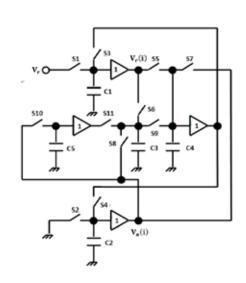

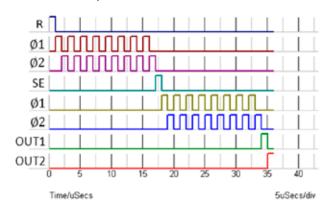

図 3.3 に、今回提案する単一利得増幅器を用いた容量比に鈍感な SC 逐次近似型 D/A 変換器を示し、スイッチ制御は表 3.1 に示すスイッチ表で行う。また、この回路は互いに重なり合わないクロックを用いて動作し、図 3.4 にクロック信号を示す。ここで、この回路の変換時間は  $36\mu s$ である。

図 3.3 単一利得増幅器を用いた容量比に鈍感な SC 逐次近似型 D/A 変換器

| S    | 1 | 2 | 3   | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

|------|---|---|-----|----|---|---|---|---|---|----|----|

| R    | 1 | 1 | 0   | 0  | 0 | 0 | 0 | 0 | 0 | 0  | 0  |

| φ1   | 0 | 0 | 0   | 0  | e | 0 | o | e | 0 | 0  | 0  |

| φ2   | 0 | 0 | *bi | bi | 0 | 0 | 0 | 0 | 1 | 1  | 0  |

| SE   | 1 | 1 | 0   | 0  | 0 | 0 | 0 | 0 | 0 | 0  | 0  |

| φ1   | 0 | 0 | 0   | 0  | o | e | e | o | 0 | 0  | 0  |

| φ2   | 0 | 0 | *bi | bi | 0 | 0 | 0 | 0 | 1 | 0  | 0  |

| OUT1 | 0 | 0 | 0   | 0  | 0 | 0 | 1 | 0 | 0 | 0  | 1  |

| OUT2 | 0 | 0 | 0   | 1  | 0 | 0 | 0 | 0 | 1 | 0  | 0  |

表 3.1 スイッチ表

※e は CNV モード( $\phi$ 1、 $\phi$ 2)における奇数を表し、o は 偶数を表す。

$%b_i$ 、 $*b_i$ は入力ビットを表し、 $b_i = 1$ の時は $*b_i = 0$ 、 $b_i = 0$ の時は $*b_i = 1$ となる。

図 3.4 クロック信号

#### 3.2.2 回路動作

R クロック :  $C_1$ に基準電圧  $V_r$ が充電され、 $C_2$ はアースによって放電される。

$\emptyset$ 1 クロック :  $C_1$  の電荷は  $C_3$ 、 $C_2$  の電荷は  $C_4$  へ転送される。

$\phi 2$  クロック :  $C_3$  と  $C_4$  が並列となり、 $C_3$  に充電されている  $V_r$  が分圧されて、それぞれの電荷は $2^{-i}V_r$  となる。 $b_i = 1$  の時、分圧された電荷は $C_2$ 、 $C_5$  へと転送される。 $C_1$  の電荷は保持される。 $b_i = 0$  の時、分圧された電荷は $C_1$  へと転送され、 $C_2$  の電荷は保持されて $C_5$  へ転送される。

$\emptyset$ 1'クロック:  $C_1$ の電荷は  $C_4$ 、 $C_2$ の電荷は  $C_3$  へ転送される。 $(\emptyset$ 1'は $\emptyset$ 1 の 2 回目のクロックである。)

$\phi$ 2'クロック:  $C_3$  と  $C_4$  が並列となり、分圧され、それぞれの電荷は $2^{-2i}V_r$ となる。 $b_i=1$  の時、分圧された電荷は  $C_4$ 、 $C_5$  へと転送される。

$C_1$  の電荷は保持される。 $b_i = 0$ の時、分圧された電荷は  $C_1$  へと転送され、 $C_2$  の電荷は保持されて  $C_5$  へ転送される。 ( $\phi$ 2' は $\phi$ 2 の 2 回目のクロックである。)

以降、 $\emptyset1$ ~ $\emptyset2$ 'クロックを4回繰り返す。

また、SE クロック**\phi2**'クロックでも R クロック $\phi$  2'クロックとほぼ同様の動作を行うが、 $C_3$  と  $C_4$  の役割が交代している。

OUT1 クロック :  $C_2$  に充電されている電荷が  $C_4$  へ、 $C_5$  に 充電されている電荷が  $C_3$  へ転送される。

OUT2 クロック:  $C_3$ と  $C_4$ が並列となり、分圧され、 $C_2$ へ 転送されたものが出力電圧である。

従来回路と提案回路と違いであるが、提案回路は R モードの CNV モードと SE モードの CNV モードを 2回行っているのに対して、従来回路は CNV モードを 1回しか行っていない。

#### 3.2.3 D/A 変換アルゴリズム

提案回路の D/A 変換において n ビット変換行う場合、基準電圧を $V_r$ 、入力ビットを $b_i$ 、 $C_3$  と  $C_4$  の間の容量不整合を $\varepsilon$ とすれば、出力電圧 $V_a$ は式(3.3)、式(3.4)の D/A 変換アルゴリズムの行列式が得られる。

Rモード:

$$\begin{pmatrix} V_r(i) \\ V_a(i) \end{pmatrix} = \begin{pmatrix} b_l + \overline{b_l} \frac{1 - (-1)^i \varepsilon/2}{2} & \overline{b_l} \frac{1 + (-1)^i \varepsilon/2}{2} \\ b_l \frac{1 - (-1)^i \varepsilon/2}{2} & \overline{b_l} + b_l \frac{1 + (-1)^i \varepsilon/2}{2} \end{pmatrix} \begin{pmatrix} V_r(i-1) \\ V_a(i-1) \end{pmatrix}$$

(3. 3)

SEモード:

$$\binom{V_r(i)}{V_a(i)} = \binom{b_l + \overline{b_l} \frac{1 + (-1)^i \varepsilon/2}{2}}{b_l \frac{1 + (-1)^i \varepsilon/2}{2}} \frac{\overline{b_l} \frac{1 - (-1)^i \varepsilon/2}{2}}{\overline{b_l} + b_l \frac{1 - (-1)^i \varepsilon/2}{2}} \binom{V_r(i-1)}{V_a(i-1)}$$

(3. 4)

#### 4. シミュレーション結果

4.1 SIMetrix によるシミュレーション結果 本実験で回路シミュレータ SIMetrix – SIMPLIS 6.10 を 使用する。表 4.1 に素子パラメータを示す。

表 4.1 素子パラメータ

| $C_1, C_2, C_5$                             | 10pF    |

|---------------------------------------------|---------|

| $C_3$                                       | 10.05pF |

| C <sub>4</sub>                              | 9.95pF  |

| $V_{\rm r}$                                 | 1V      |

| ε/2(C <sub>3</sub> とC <sub>4</sub> の間の容量不整合 | 0.5%    |

| をεとおく)                                      |         |

| V <sub>on</sub> (スイッチオン時の電圧)                | 3V      |

| V <sub>off</sub> (スイッチオフ時の電圧)               | 2V      |

| R <sub>on</sub> (スイッチオン時の抵抗)                | 1kΩ     |

| R <sub>off</sub> (スイッチオフ時の電圧)               | 100ΤΩ   |

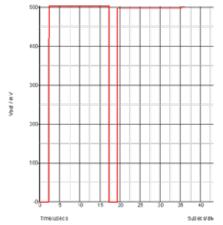

まず、特徴的な入力信号 10000000、01010101、10101010、 11111111 の出力電圧の波形を図 4.1 に示す。

図 4.1(a) 入力信号 10000000 のときの出力電圧

図 4.1(b) 入力信号 01010101 のときの出力電圧

図 4.1(c) 入力信号 10101010 のときの出力電圧

図 4.1(d) 入力信号 111111111 のときの出力電圧

各波形より、どの入力コードでも正常に動作している ことが確認できる。

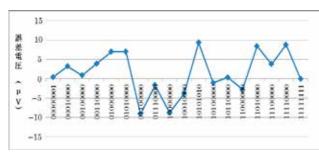

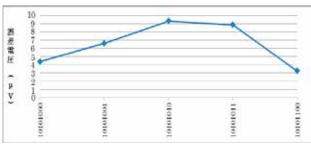

同様にシミュレーションを行い、出力電圧の理論値と 測定値の誤差を求める。測定を行う入力信号は、入力信 号 00000001~111111111 の 255 パターンを約 16 間隔で区 切ってシミュレーションを行う。シミュレーション結果 の表と誤差電圧のグラフを表 4.2、図 4.2 に示す。

表 4.2 入力信号 00000001~11111111(約 16 間隔)の シミュレーション結果

|          | 7 1 1 1    | ノコノ加木       |        |

|----------|------------|-------------|--------|

| 入力信号     | 理論値(V)     | 測定値(V)      | 誤差(µV) |

| 00000001 | 0.00390625 | 0.003905835 | 0.42   |

| 00010000 | 0.0625     | 0.062496785 | 3.22   |

| 00100000 | 0.125      | 0.124999144 | 0.86   |

| 00110000 | 0.1875     | 0.187496104 | 3.90   |

| 01000000 | 0.25       | 0.249993022 | 6.98   |

| 01010000 | 0.3125     | 0.312493014 | 6.99   |

| 01100000 | 0.375      | 0.375009105 | -9.11  |

| 01110000 | 0.4375     | 0.437501655 | -1.65  |

| 10000000 | 0.5        | 0.500008787 | -8.79  |

| 10010000 | 0.5625     | 0.562503829 | -3.83  |

| 10101010 | 0.6640625  | 0.664053162 | 9.34   |

| 10100000 | 0.625      | 0.625001078 | -1.08  |

| 10110000 | 0.6875     | 0.687499658 | 0.34   |

| 11000000 | 0.75       | 0.750002737 | -2.74  |

| 11010000 | 0.8125     | 0.812491558 | 8.44   |

| 11100000 | 0.875      | 0.874996244 | 3.76   |

| 11110000 | 0.9375     | 0.937491175 | 8.82   |

| 11111111 | 0.99609375 | 0.996093809 | -0.06  |

図 4.2 入力信号 00000001~11111111 (約 16 間隔)の誤差電圧

表 4.2、図 4.2 より、入力信号 10101010 の時に理論値が 0.6640625V に対して測定値が 0.664053162V となり、誤 差電圧が  $9.34\mu$ V で最大となった。次に、入力信号 10101010 付近を更に細かくシミュレーションし、より誤 差が大きい部分がないか確認する。シミュレーション結果の表と誤差電圧のグラフを表 4.3、図 4.3 に示す。

表 4.3 入力信号 10101000~10101100 の シミュレーション結果

| 入力信号     | 理論値(V)     | 測定値(V)      | 誤差(µV) |

|----------|------------|-------------|--------|

| 10101000 | 0.65625    | 0.656245609 | 4.39   |

| 10101001 | 0.66015625 | 0.660149638 | 6.61   |

| 10101010 | 0.6640625  | 0.664053162 | 9.34   |

| 10101011 | 0.66796875 | 0.667959884 | 8.87   |

| 10101100 | 0.671875   | 0.671871749 | 3.25   |

図 4.3 入力信号 10101000~10101100 の誤差電圧

表 4.3、図 4.3 より、表 4.2、図 4.2 の結果と同様に入力信号 10101010 の時に誤差電圧が最大であることが確認できる。

#### 4.2 分解能についての考察

シミュレーションで得られた最大の誤差電圧からその D/A 変換器の分解能を求める。ここで、誤差電圧 $\Delta V_a$ と 分解能 n の関係式を式(4-1)に示す。

$$\Delta V_a < \frac{1}{2^{n+1}} V_r \tag{4.1} \label{eq:delta_var}$$

シミュレーションの結果より、入力信号 10101010 の時に誤差電圧が最大であるので、式(4.1)の誤差電圧 $\Delta V_a$ に 9.34 $\mu V$ 、基準電圧 $V_r$ に 1V をそれぞれ代入する。

$$\begin{split} \Delta V_{a} < \frac{1}{2^{n+1}} V_{r} \\ 9.34 \times 10^{-6} < \frac{1}{2^{n+1}} \\ 2^{n} < \frac{1}{2 \times 9.34 \times 10^{-6}} \\ \log_{2} 2^{n} < \log_{2} 2^{n} \frac{1}{2 \times 9.34 \times 10^{-6}} \\ n < 15.7 \end{split}$$

計算結果より、提案回路の分解能は15ビットとなることがわかった。

n = 15 ビット

一方、従来回路の分解能は、文献[6]より9ビットであることが確認されているため、分解能を比較すると9ビットから15ビットへ改善することができた。

#### 5. 結論

本実験では、単一利得増幅器を用いた容量比に鈍感な SC 逐次近似型 D/A 変換器を提案し、回路シミュレータ SIMetrix によるシミュレーションを行った。本論文では、回路の基本構成や D/A 変換の特性について述べ、得られた実験結果より考察を行った。

実験結果として、2つのコンデンサ間に容量不整合を含ませてシミュレーションを行った結果、入力信号10000000、01010101、10101010、111111111 の時に出力電圧の理論値と図 4.1 のシミュレーションより得られた測定値がほぼ同じ値となっており、容量不整合に影響しない正確な D/A 変換が行われていることが確認できた。また、図 4.2、図 4.3、表 4.2、表 4.3 より、入力信号 00000001~111111111 のうち、出力電圧の理論値と測定値の誤差が最大となるのは入力信号 10101010 の時で、式(4.1)より、提案した D/A 変換器の分解能は 15 ビットであることがわかった。従来の D/A 変換器と比較すると、分解能は 9

ビットであるため大きく改善できたといえる。

よって、今回提案した単一利得増幅器を用いた容量比に鈍感な SC 逐次近似型 D/A 変換器は、従来よりも分解能を改善することができ、精度が向上したと考えられる。今後の課題としては、提案した D/A 変換器は従来の D/A 変換器よりも変換時間が 2 倍かかっているので、分解能を改善しつつ変換時間を上げることが必要である。

#### 7. 参考文献

- 1) 相良 岩男: "AD/DA 変換回路入門", 日刊工業新聞社, 1991

- 2) 中山謙二 著,"SC 回路網の設計と応用", 東海大 学出版社 (1985).

- 3) 武部幹・岩田穆・国枝博昭・高橋宣明 著, "スイッチトキャパシタ回路", 現代工学社 (1984)

- 4) 白土義男 著, "たのしくできるやさしいアナログ回路の実験", 東京電機大学出版局 (1994)

- 5) 鈴木茂昭 著, "アナログ・スイッチの使い方", CQ 出版社 (1980)

- 6) Watanabe Kenzo, Temes Gabor, Tagami Tomohisa, "A New Algorithm for Cyclic and Pipeline Data Conversion", Shizuoka University (1990)