## 演算増幅器を用いた容量比に鈍感な SC 逐次近似型 AD 変換器

森山 和貴 a) · 松本 寛樹 b)

# SC Successive Approximation A/D Converter Insensitive to Capacitance Ratio and Using Operational Amplifier

Kazuki MORIYAMA, Hiroki MATUMOTO

### Abstract

This paper shows an improved A/D converter insensitive to capacitance mismatch. By using operational amplifier, error caused by it is reduced and resolution is estimated to 14bits.

Converter operation is confirmed on SIMetrix.

Keywords: Swiched-capacitor, A/D Converter, capacitance ratio, operational Amplifer.

#### 1 序論

1990年代から、ディジタル技術の高度化により、コンピュータは急速な発展を遂げてきている。コンピュータは、その本来の意味する「計算機」という枠組みにとどまらず、あらかじめソフト的もしくはハード的に組み込まれたプログラムに基づき、入力されるデータの観測、蓄積、処理やそれらの結果に応じた所望のデータの出力などを自由自在にそして短時間で処理できる。

しかしながら、コンピュータで扱えるデータは『0』と『1』の 2 つの値で表されるディジタル信号だけである。自然界に存在している、温度、速度、圧力、流れなどの物理量はほとんどアナログ量であり、また、発振機によって作られた正弦波、三角波、方形波や人間の音声などもアナログ量である。

したがってこのアナログ量をディジタル信号、あるいはディジタル信号をアナログ量に変換することで、コンピュータの幅広い応用が可能になる。一般に、この変換はそれぞれ A/D 変換(analog to digital conversion)、D/A 変換(digital to analog conversion)と呼ばれる

本研究では、オペアンプと電圧比較器を用いて、キャパシタの不整合による誤差を低減した AD 変換回路を制作し、SIMetrix を用いて動作比較検討する。

a)大学院電気電子工学専攻 b)工学部准教授

### 2 A/D 変換器

### 2.1 A/D 変換器過程

A/D 変換とは、アナログ量からディジタル信号に変換することである。この A/D 変換を通信関係では符号化や変調と呼ばれる。これを実現する電子回路が A/D 変換器である。

A/D 変換の過程は前置フィルタを通ったあとアナログ 量を標本化、量子化、符号化の順に行うことによってディ ジタル信号に変換される。

#### 2.1.1 標本化

標本化とは、連続的なアナログ量の振幅値をある離散的な周期 T(周波数 fs=1/T)を基に区切り、アナログの振幅の瞬間値インパルス信号を取り出していくことである。これを標本化またはサンプリングと呼ぶ。fs は標本化周波数である。

標本化によるインパルス列(デルタ関数列)は PAM(パルス振幅変調)や標本化信号と呼ばれる。この PAM はアナログ量をパルス波で変調した信号となり、周波数スペクトルは nfs を基準に上側波帯と下側波帯に分けられる。

### 2.1.2 量子化

量子化(quantizing)とは、保存されているアナログ電圧 Vrがある基準とすると電圧 Vs の何倍になっているか判断し、倍数値を整数値に丸めることである。その丸めによって生じた誤差は量子化誤差(quantize-tion error)と呼ばれ、A/D 変換では避けられない誤差である。また、基準電圧によって異なる整数値になる。整数値に丸める方法としては切り捨て法、切り上げ法、四捨五入法の三通りが考えられ

る。一般的には、二乗平均誤差が最も小さくなる四捨五入 法が用いられる。

### 2.1.3 符号化

符号化(coding)とは、量子化によって丸められた整数値を2進コードに変換することである。A/D変換器に入力される電圧はユニポーラ形とバイポーラ型とがある。

ユニポーラ形とは、例えば  $0\sim+5[V]$ のように正の極性だけを持つものをいい、バイポーラ形とは、例えば- $2.5\sim+2.5[V]$ のように両極性を持つものをいう。

#### 2.2 A/D 変換器の諸特性

#### 2.2.1 入出力特件

A/D 変換器の入出力特性は横軸にアナログ入力電圧、縦軸に出力のディジタルコードを取ったものである。量子化誤差が最小になるように-1/2LSB のオフセットを与えた特性を図に示した。この図 6 ではフルスケールレンジ (FSR) が 8[V]であり、FSR の 8等分の値 1[V]ごとの電圧をオフセット(=-0.5[V])分ずらしてディジタルビットで示したものである。0[V]、0.5[V]以降は 1[V]毎に、1つのディジタルビットずつ変化する。例えば、0.5[V]  $\leq$  Va<1.5[V]に示す範囲内のディジタルビットは"001"である。また、このときの分解能は

1LSB=8/2<sup>3</sup>=1[V]

であり、量子化誤差は 1/2LSB(=0.5[V])である

### 2.2.2 A/D 変換器の仕様

A/D 変換器の仕様について各項目ごとに説明する。

分解能 A/D 変換における分解能(resolution)はディジタル信号の 1 段階の変化に対する最小の識別可能な出力変化をいう。たとえば、8[V]の FSR で 3 ビットの分解能は $8/2^3=1[V]$ である。この分解能を 1LSB あるいは $\triangle$ と表記する。あるいは  $12.5\%(1/2^3)$ ととってもよい。10 ビットならば分解能は約  $0.1\%(1/2^{10})$ である。

精度 A/D 変換器の精度は量子化誤差や外部からの雑音 および素子のばらつきなどに大きく影響される。通常、量子化誤差は $\pm 1/2$ LSB ではあるが、仕様として示される精度はそれ以外の誤差の合計として表される。精度の代表値は FSR の $\pm 0.02$ %である。A/D 変換器のビット長はこれらを考慮して決められている。

変換時間 A/D 変換器における変換時間(conversion time)は、変換開始命令を与えてから実際にディジタル出力を終えるまでの時間である。変換時間の代表値は高速なもので $3\sim5[ns]$ 、低速なもので数[ms]である。

### 2.3 逐次平均型 ADC

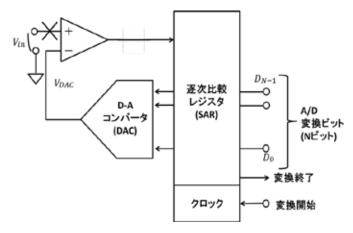

図1に示すように、逐次比較型 A-D コンバータは、コ

ンパレータ(比較器)、逐次比較レジスタ(SAR)、クロック 発生器の4ブロックから構成される。実際のICでは、変 換動作の間入力電圧を保持するサンプル&ホールド・アン プが×に示す箇所にはいる。

変換の手順は上皿天秤を使用した計測方法と同様で、分解能が 4 ビットの場合、1g、2g4g、8g といった 2 進数の重みづけ(バイナリウエイト)を持ったおもりを用意し、天秤の片方の皿に被測定物を乗せる。

仮に $D_3 \sim D_0$ の 4 ビットとすると、最も重いおもりの 8 g は、最も重みづけの大きいビット(MSB)の $D_3$ に相当し、最も軽い 1g は、最も重みづけの小さいビット(LSB)の $D_0$  となる。

被測定物の重さを 5g の変換手順を次に示す。

- ① 最も重いおもりを、もう一方の天秤皿に乗せて比較する。

- この場合は、おもりの合計>被測定物なので、8g は取り去り、 $D_3$ ビットは'0'とする

- ② 8g の次に重い 4g のおもりを天秤皿に乗せて比較する。今度は、おもり合計<被測定物なので、4g はのせたままにして $D_2$ ビットを'1'にする。

- ③ 4g の次に重い 2g のおもりを追加(合計 6g)して比較すると、おもり合計>被測定物なので、2g のおもりは取り去って $D_1$ ビットを'0'にする。

- ④ 最後に、一番軽いおもり 1g を天秤皿に乗せて比較すると、天秤皿が平衡したので、 $D_0$ ビットを'1'にする。このときのおもりの合計が被測定物の重さになるので、最終的な出力データは'0101'が得られる。

図1 逐次平均型 ADC の構成

### 3 演算増幅器を用いた容量比に鈍感な SC 逐次近 似型 A/D 変換器

#### 3.1 従来回路

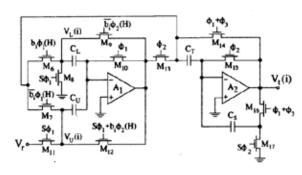

図2に従来回路である演算増幅器を用いたSC逐次近似型 A/D 変換器の回路図を示す。この回路図は Vr に入力された電圧を変換し、出力する回路図である。

キャパシタの容量値は  $C_U$ =10pF, $C_S$ =10pF, $C_T$ =9.95pF、 $C_S$ =10.05pF、と設定する。 $C_3$ と  $C_4$ は容量不整合 1%となっている。なお、分解能は 9bit である。

### 3.2 提案回路

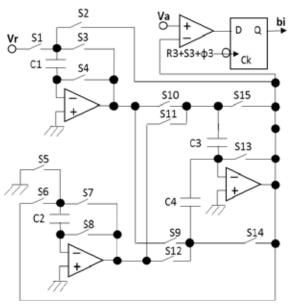

図 3 今回提案する演算増幅器を用いた容量比に鈍感な SC 逐次近似型 A/D 変換器を示す。また回路のスイッチ制 御は表によって行う。

### 3.2.1 回路構成

図3回路構成は

$C_1 = C_2 = C_u = 10[pF] \quad ,$

$C_3 = (1 + \mathcal{E}/2), Cu$

$C_4=(1-\varepsilon/2) Cu$ ,

$\varepsilon = 1[\%]$

オペアンプの電圧増幅率 1(Av=1)

図 3 演算増幅器を用いた容量比に鈍感な逐次近似型 A/D 変換器

### 3.2.2 回路動作

図3路の動作において、表1に示すアルゴリズムにおける各クロック毎の回路状態と各素子の電圧などを次に示す。

$R_1$ : 基準電圧  $\operatorname{Vr}$  が $C_1$ に充電され、 $C_2$  では接地とつなが り放電される。

$R_2$ : C と $C_2$ に充電された電荷が $C_4$ と $C_3$ に転送される。

$R_3$ : 基準電圧 Vr が $C_1$ に充電、 $C_2$  は放電され、 $C_3$  と $C_4$ が 並列接続となり両端電圧が等しくなる。

$\emptyset_2$ : 奇数回目では $C_1$ の電荷が $C_4$ に、 $C_2$ の電荷が $C_3$ に転送される。

偶数回目では $C_1$ の電荷が $C_3$ に、 $C_2$ の電荷が $C_4$ に転送される

$\phi_3$ :  $C_3$ と $C_4$ が並列接続となり両端電圧が等しくなる。

$\phi_1 \sim \phi_3$ を 16 回繰り返す。

$S_1$ : 基準電圧  $\operatorname{Vr}$  が $C_1$ に充電され、 $C_2$  では接地とつながり放電される。

$S_2$ :  $C_1$ と $C_2$ に充電された電荷が $C_3$ と $C_4$ に転送される。

$S_3$ : 基準電圧  $V_r$  が $C_1$ に充電、 $C_2$  は放電され、 $C_3$ と $C_4$ が 並列接続となり両端電圧が等しくなる。

$\emptyset_2$ : 奇数回目では $C_1$ の電荷が $C_4$ に、 $C_2$ の電荷が $C_3$ に転送される。

偶数回目では $C_1$ の電荷が $C_3$ に、 $C_2$ の電荷が $C_4$ に転送される。

$\emptyset_3$ :  $C_3$ と $C_4$ が並列接続となり両端電圧が等しくなる。

$\phi_1 \sim \phi_3$ を 16 回繰り返す。

#### 4 シミュレーション結果

動作原理を確認するために、SIMetrix を用いて実験を行った。基準電圧 $V_r$ は 1[V]に設定している。CONV1 は一度目の変換、CONV2 は二回目の変換、平均化は CONV1 と CONV2 を平均した値であり、誤差ビットは真値から平均値を引いたものである。

### 4.1 SIMetrix によるシミュレーション結果

誤差ビット:0000 0000 0000 0000

### Va=666.6565[mV]のとき

Va=666.6565[mv]に設定したときの波形を図 13 に示し、 その時得られたビットを次に示す。図 3 において上のグラ フは比較器において入力電圧と比較する電圧、中央のグラ フは出力ビット、下のグラフは D-FF を動作させるクロッ クを示す。 CONV1:1010 1010 1111 0000 CONV2:1010 1010 0110 0000 平均化:1010 1010 1010 1000 誤差ビット:0000 0000 0000 0010

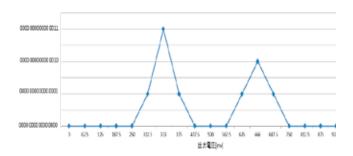

出力電圧  $0\sim937.5[\text{mV}]$ まで 62.5[mV]刻みで測定した結果を表2にまとめた。

図3は表2のデータを踏まえて、縦軸を誤差ビット、横軸を出力電圧でとったグラフである。

### 表 1 測定結果

| 出力電圧[mV] | 理想ビット               | 出力ビット               | 誤差ビット               |

|----------|---------------------|---------------------|---------------------|

| 0        | 0000 0000 0000 0000 | 0000 0000 0000 0000 | 0000 0000 0000 0000 |

| 62.5     | 0001 0000 0000 0000 | 0001 0000 0000 0000 | 0000 0000 0000 0000 |

| 125      | 0010 0000 0000 0000 | 0010 0000 0000 0000 | 0000 0000 0000 0000 |

| 187.5    | 0011 0000 0000 0000 | 0011 0000 0000 0000 | 0000 0000 0000 0000 |

| 250      | 0100 0000 0000 0000 | 0100 0000 0000 0000 | 0000 0000 0000 0000 |

| 312.5    | 0101 0000 0000 0000 | 0101 0000 0000 0001 | 0000 0000 0000 0001 |

| 333      | 0101 0101 0101 0101 | 0101 0101 0101 1000 | 0000 0000 0000 0011 |

| 375      | 0110 0000 0000 0000 | 0110 0000 0000 0001 | 0000 0000 0000 0001 |

| 437.5    | 0111 0000 0000 0000 | 0111 0000 0000 0000 | 0000 0000 0000 0000 |

| 500      | 1000 0000 0000 0000 | 1000 0000 0000 0000 | 0000 0000 0000 0000 |

| 562.5    | 1001 0000 0000 0000 | 1001 0000 0000 0000 | 0000 0000 0000 0000 |

| 625      | 1010 0000 0000 0000 | 1001 1111 1111 1111 | 0000 0000 0000 0001 |

| 666      | 1010 1010 1010 1010 | 1010 1010 1010 1000 | 0000 0000 0000 0010 |

| 687.5    | 1011 0000 0000 0000 | 1010 1111 1111 1111 | 0000 0000 0000 0001 |

| 750      | 1100 0000 0000 0000 | 1100 0000 0000 0000 | 0000 0000 0000 0000 |

| 812.5    | 1101 0000 0000 0000 | 1101 0000 0000 0000 | 0000 0000 0000 0000 |

| 875      | 1110 0000 0000 0000 | 1110 0000 0000 0000 | 0000 0000 0000 0000 |

| 937.5    | 1111 0000 0000 0000 | 1111 0000 0000 0000 | 0000 0000 0000 0000 |

### 図3 測定結果

### 5 考察

今回の実験回路では、容量不整合の影響で CONV1 と CONV2の二つの試行を単体で捉えると Va=500[mV]に設定した場合では、図 12 より上位ビットから数えて 8bitまでしか A/D 変換の結果が正しくないが、CONV1 と CONV2 をまとめて一つの試行と捉えそれぞれの値を平均化すれば、Va=333.32825[mV]、Va=666,6565[mV] と設定した場合に、上位ビットから数えて 14bit まで A/D 変換の結果が正しくおこなわれる。このことから従来回路では分解能が 9bit であり、提案回路は容量比 1%に対して分解能が 14bit なので本回路は容量比に鈍感であるとわかる。

今回、Va=1000[mV]のデータを含んでいないのは 1000[mV]を二進数表現で表すのが不可能であり、回路の 精度を上げた場合でも必ず誤差を生じるからである。

今後の課題はとして、逐次近似型の短所である変換時間 をいかに短縮するかと素子数の減少が挙げられる。

### 6 参考論文

- [1] 千原国宏 著, 'パソコン世代の電子回路入門', コロナ社(1991)

- [2] 菊池正典 著, 'これならわかる電子回路', ナツメ社(2011)

- [3] 相良岩男 著, 'AD/DA 変換回路入門', 日刊工業(1991)

- [4] 樋口龍雄 著, 'アナログディジタル変換', 日刊 工業(2005)