# Si<sub>1-x</sub>Ge<sub>x</sub> S/D p-MOSFET への電子線照射による 電気的特性への影響の評価

中島 敏之 <sup>a,b)</sup>・出本 竜也 <sup>c)</sup>・米岡 将士 <sup>d)</sup>・角田 功 <sup>e)</sup>・高倉 健一郎 <sup>f)</sup>・大山 英典 <sup>g)</sup>

E. Simoen <sup>h)</sup>・C. Claevs <sup>i,j)</sup>・吉野 賢二 <sup>k)</sup>

# Radiation Damage in Electrical Characteristic of Si<sub>1-x</sub>Ge<sub>x</sub> S/D p-MOSFET by Electron Irradiation

Toshiyuki NAKASHIMA, Tatsuya IDEMOTO, Masashi YONEOKA, Isao TSUNODA, Kenichiro TAKAKURA, Hidenori OHYAMA, Eddy SIMOEN, Cor CLAEYS and Kenji YOSHINO

#### **Abstract**

The effect of 2-MeV electron irradiation of Si<sub>1-x</sub>Ge<sub>x</sub> S/D p-MOSFETs with different Ge concentration and gate length is studied. Before electron irradiation, effect of strain in Si channel is clearly observed that the maximum hole mobility increase and threshold voltage negative shift. After electron irradiation, the maximum hole mobility decreases with increasing electron fluence for all samples. In particular, in the case of high strain sample which have high Ge concentration and short channel, the maximum hole mobility drastically decreases by electron irradiation. Furthermore, it clearly observed that the amount of threshold voltage negative shifts which due to strain Si channel has decreased by electron irradiation. These degradations can be explained both by the lattice defects and the stress relaxation in the Si channel created by atomic displacements.

Keywords: Strained Si, Radiation damage, MOSFET, Electron, Hole mobility

#### 1. はじめに

微細化に伴う高集積化,新構造や新材料の開発によるデバイス性能の向上に向けた取り組みは世界各地でなされており,高性能化,多機能化された半導体デバイスは多分野へ利用されている.近年では高エネルギー加速器や原子炉内部,人工衛星などの過酷な放射線環境下での利用も半導体デバイスにおける重要な用途のひとつである.常に放射線に曝されるような環境下

においては放射線の影響による電気的特性劣化やデバイスの破壊が起こることが知られており、材料や構造に応じて劣化する <sup>1)</sup>. そのため、過酷な放射線環境下での用途に利用される可能性がある半導体デバイスの開発においては放射線による劣化の振舞いを評価することは非常に重要である <sup>1)</sup>.

一方で、集積回路構成の中心となっている Si を材料とした CMOS デバイスにおいては、スケーリング則に沿った微細化による性能向上に物理的な限界が近づいている。そこで、新しい構造や材料を利用したデバイスの開発が進んでおり  $^{2)}$ 、その手法の一つとして注目されているものに、歪 Si をチャネルに用いたデバイスがある。これは、SiGe や SiN をストレッサーとして外部から Si チャネル部に歪による応力を印加したデバイスであり、印加された応力により移動度が向上することが知られている  $^{3-6)}$ . ゲートサイズの微細化を行わずとも性能向上が図れると共に、従来の Si MOSFET の拡散工程を応用して実用化できる事から、今後の主要技術の一つとして研究、実用化が進められている.

今後, 歪 Si チャネルを持つデバイスが高性能の半導体デバイスとして, 過酷な放射線環境下での用途に利

- a) 宮崎大学 農学工学総合研究科大学院生

- b)中央電子工業株式会社 製品技術 Gr

- c)熊本高等専門学校 電子情報システム工学専攻科生

- d)熊本高等専門学校 技術センター職員

- e)熊本高等専門学校 情報通信エレクトロニクス工学科助教

- f)熊本高等専門学校 情報通信エレクトロニクス工学科准教授

- g)元熊本高等専門学校 情報通信エレクトロニクス工学科教授

- h) Belgium imec senior researcher

- i) Belgium imec Director advanced semiconductor technologies

- j) KULeuven Professor

- k)宫崎大学 電気電子工学科准教授

用されていくことは十分に想定されるが、その耐放射線性に関する研究報告はほとんどなされていない。そこで、 $\Xi$  Si チャネルを用いた Si<sub>1-x</sub>Ge<sub>x</sub> Souse/Drain (S/D) p-MOSFET に電子線を照射した場合におこる電気的特性の劣化について実験を行ったので報告する。

### 2. 実験

#### 2.1 対象サンプル

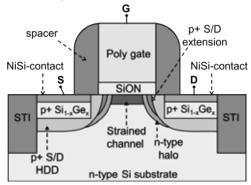

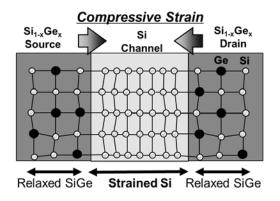

図1に今回の実験に使用した  $Si_{1-x}Ge_x$  S/D p-MOSFET の断面図を示す. 特徴として Source 及び Drain 部に SiGe を使用しており、格子定数の違いにより SiGe S/D -Si チャネルの境界部に歪が生じる. この歪により Si チャネルに圧縮応力が加わる構造(図 2)になっており、印加された圧縮応力が導電に寄与する正孔の実効 移動度を向上させ、従来の Si チャネルデバイスと比較して高速動作をすることが出来る. 今回使用したサンプルのサイズ、Ge 濃度を表 1 に示す.

図 1. Si<sub>1-x</sub>Ge<sub>x</sub> S/D p-MOSFET の断面図.

図 2. Si<sub>1-x</sub>Ge<sub>x</sub>/Si 界面における圧縮応力印加の概念図.

表 1. デバイスサイズ及び Ge 濃度

| 公 1. / 1 / / / / / / / / / / / / / / / / |              |

|------------------------------------------|--------------|

| ゲート長 L(μm)                               | 0.25, 0.3, 1 |

| ゲート幅 W(μm)                               | 10           |

| 酸化膜厚: SiON(μm)                           | 1.5          |

| Ge 濃度 x                                  | 0, 0.2, 0.3  |

#### 2.2 放射線照射条件

照射する放射線種は電子線を使用した.電子線は日本原子力研究開発機構・高崎量子応用研究所の電子線2号加速器を用い,照射用の台(図3)の上に置いたサンプルにゲート直上から垂直に照射した.電子線の照射条件は表2のとおりである.

図3. 電子線加2号速器の照射台外観.

表 2. 電子線照射条件

| 27 = 12.1 (\$3,000,33,5)(1) |                                                                                |  |

|-----------------------------|--------------------------------------------------------------------------------|--|

| 照射装置                        | 高崎量子応用研究所 電子線 2 号加速器                                                           |  |

| 加速エネル                       | 2 MeV                                                                          |  |

| ギー                          |                                                                                |  |

| 照射温度                        | 室温                                                                             |  |

| 照射時バイアス                     | 無バーグス                                                                          |  |

| 照射線束量                       | $4.68 \times 10^9 \text{e/cm}^2\text{s}$                                       |  |

| 照射量                         | $1 \times 10^{17}$ , $2 \times 10^{17}$ , $5 \times 10^{17}$ e/cm <sup>2</sup> |  |

#### 2.3 電気的特性評価

電子線照射によるデバイスへの影響を評価するため、デバイスの入力( $I_{DS}-V_{GS}$ )特性を用いた. 測定の条件として  $V_{DS}=-25$  mV,  $V_{GS}=-1.2\sim0.4$  V とし、電子線照射前と照射後の違いに着目した. 特性の測定には熊本高等専門学校所有の半導体パラメーターアナライザ4156C を用い、測定結果より最大相互コンダクタンス( $g_{m max}$ )及び最大正孔移動度( $\mu_{p max}$ )を数式(1),(2)より算出した.

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}} \tag{1},$$

$$\mu_{p\,max} = \frac{g_{m\,max}\,L}{W\,C_0\,V_{DS}} \tag{2},$$

$I_{DS}$  はドレイン電流,  $V_{GS}$  はゲート電圧, L はゲート長, W はゲート幅,  $C_0$  はゲート酸化膜容量,  $V_{DS}$  はドレイン電圧である。また、測定した入力特性から外挿した直線から閾値電圧  $V_{TH}$  を求めた。

#### 3. 実験結果及び考察

#### 3.1 Ge 濃度依存性

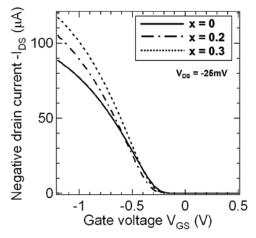

まず電子線による劣化と Ge 濃度 x の関係を議論する。図 4 に x=0, 0.2, 0.3 のサンプルの電子線照射前の入力特性を示す。全てのサンプルで,p-MOSFET の動作が確認され, $V_{GS}\!=\!-0.6V$  以下の領域において xの増加に伴い  $I_{DS}$ が増加している。

図 4. 電子線照射前の Si<sub>1-x</sub>Ge<sub>x</sub> S/D p-MOSFET の 入力特性.

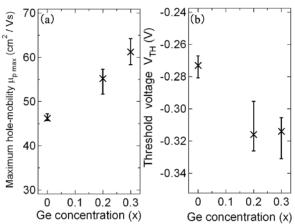

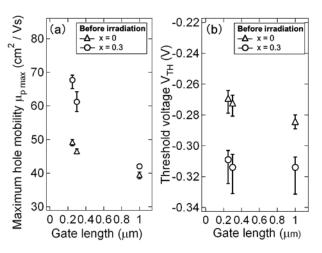

図 5. 電子線照射前の(a)最大正孔移動度と (b)閾値電圧のGe濃度依存性.

図 5(a), (b)に入力特性の結果から算出した,最大正孔移動度 $\mu_{p \, max}$  と閾値電圧  $V_{TH}$  を示す. $\mu_{p \, max}$  は x が増加すると共に増加する傾向を示した.これは Ge の増加と共に正孔移動度の向上効果が高まったことを示す.つまり Si チャネル部への圧縮応力が増加したことを示唆しており,Gonzalez らの Ge 濃度と応力の関係性を示した報告と一致する  $^{7)}$ . また,電子線照射前の  $V_{TH}$  は S/D 部に Ge を導入することでマイナス側へシフトしていることが確認された.正孔移動度向上のためにチャネルに加えた応力が  $V_{TH}$  に影響を与えていることを示唆しており,Claeys らの報告とも一致している  $^{8)}$ . 以上の結果より,電子線照射前のサンプルにおいて,

電気的特性に Ge 濃度依存性が見られることが確認された.

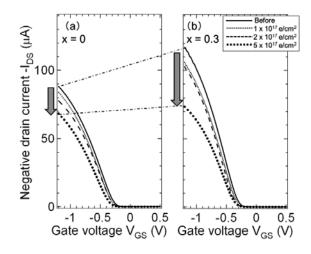

次に電子線照射後の電気的特性劣化とGe濃度の関係について述べる。図6(a), (b)に電子線照射後のx=0, 0.3のサンプルの入力特性を示す。同じ $V_{GS}$ の値で比較すると,Geの濃度に関係なく電子線照射後には照射前と比較して $I_{DS}$ が減少することが確認された。照射量毎変化を見ると,照射量の増加に伴い $I_{DS}$ の減少量が増加した。また,Ge濃度で比較するとx=0.3のサンプルの方が $I_{DS}$ の減少量が大きく,照射量 $5 \times 10^{17}$   $e/cm^2$ においては,照射前に見られた $I_{DS}$ の差異がx=0と0.3の間でほぼ同等になっている。

図 6. 電子線照射後の(a)x=0と(b)x=0.3のSi<sub>1-x</sub>Ge<sub>x</sub>S/D p-MOSFETの入力特性.

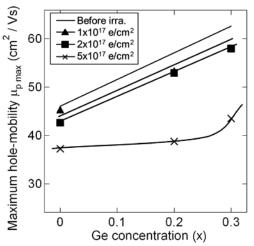

このGe導入有無による入力特性劣化の違いの要因を 検証するため、算出した $\mu_{p max}$ 及び $V_{TH}$ をGe濃度の関数 として整理し議論する. 図7に示したμ<sub>n max</sub>の電子線照 射量毎の変化を見ると,  $2 \times 10^{17} \, e/cm^2$ 以下の照射量では 全体的にμ<sub>n max</sub>が低下しているが、Ge濃度に比例する傾 向がみられた. これは圧縮応力による正孔移動度の向 上効果を示唆しており,  $2 \times 10^{17} \, \text{e/cm}^2$ 以下の照射量では 正孔移動度の向上に寄与する圧縮応力が保持されてい ることを示している. また,  $5 \times 10^{17} \text{ e/cm}^2$ の照射量で は、Ge濃度に比例した移動度増加の傾向が変化し、x =0.2のサンプルの $\mu_{p max}$  はx=0とほぼ同等になった. 更に, x=0.3ではx=0に対し高い $\mu_{n,max}$ を示したものの, 照射前と比べるとサンプル間の差が減少していること が分かった. これらの結果は,  $5 \times 10^{17} \text{ e/cm}^2$ の電子線 照射により, 歪Siチャネル部に加わる圧縮応力が低下 もしくは消滅したことを示している. x=0.2と0.3で比 較すると、より高い圧縮応力を持つx=0.3のサンプル がより高い正孔移動度を維持できていることから、電 子線照射による圧縮応力の消滅や低下はGe濃度に依存 しているといえる.

図7. 電子線照射後の最大正孔移動度のGe濃度依存性.

図 8. 電子線照射前後の閾値電圧のGe濃度依存性 (照射量:5 x 10<sup>17</sup>e/cm<sup>2</sup>).

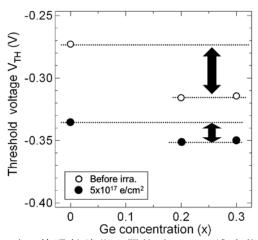

$\mu_{p max}$ において $5 \times 10^{17} e/cm^2$ の電子線照射で圧縮応力 低下を示唆する結果が得られたことから, この照射量 に着目し、電子線照射前後でのV<sub>TH</sub>の値をGe濃度毎に 図8に整理した.  $V_{TH}$ は全てのGe濃度のサンプルおいて 電子線照射後にマイナス側にシフトしている. MOSFETに電子線が照射された場合には, 照射により ゲート酸化膜内部及び酸化膜とSiチャネルの界面付近 に捕獲される電荷の影響を受け、V<sub>TH</sub>がマイナス側へシ フトすることが既に知られている<sup>9)</sup>. この捕獲電荷によ る影響は、ゲート酸化膜厚や照射エネルギーに依存す る10)が、今回の実験においては、ゲート酸化膜及びチ ャネル界面の構造は全て同一にしていることから、捕 獲電荷による影響は変わらず, 同程度のマイナスシフ トを示すと考えられる. しかし、Ge導入有無での差を 検証すると, x=0.2もしくは0.3のサンプルとx=0のサ ンプルとの間に照射前に存在したVTHの差が小さくな っている. 照射前の差は圧縮応力に起因するマイナス シフトであり8),前述の移動度から示唆された歪Siチャ ネル部の圧縮応力低下もしくは消滅が起きているとす ると、応力による $V_{TH}$ のマイナスシフトも緩和されると考えられる.この $V_{TH}$ の変動からも $\mu_{p \ max}$ の減少と同様に電子線照射による圧縮応力の低下が示唆される.

#### 3.2 ゲート長依存性

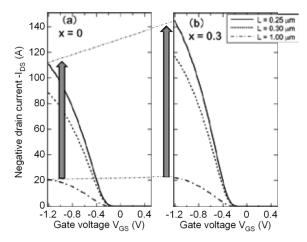

次にGe濃度と同様に歪Siチャネル部に印加される圧縮応力を変化させる要素の一つであるゲート長に着目し、ゲート長の違いが電子線照射前後の入力特性に与える影響について議論する. 各ゲート長(L=0.25, 0.3, 1 $\mu$ m)におけるx=0, 及び0.3の電子線照射前の入力特性を図9(a), 及び(b)に示す. x=0, 0.3のサンプル共にゲート長の縮小に伴い $I_{DS}$ の値が増加した. これは微細化によるMOSFETの性能向上効果によるものである. また, x=0と0.3の結果を比較すると,後者の $I_{DS}$ 向上効果が大きいことが分かる. x=0.3のサンプルにおいてはゲート長縮小による向上効果の他に,圧縮応力による向上効果が加わったと考えられる.

図9. 各ゲート長における電子線照射前の(a)x=0と(b)x=0.3の入力特性.

微細化によるIps向上効果の違いをより詳しく検証す るため, $\mu_{p max}$ と $V_{TH}$ を算出し図10(a),(b)にゲート長の 関数として整理した.この結果,全てのゲート長にお いて、Ge導入によりμ<sub>n max</sub>が高い値を示している.これ はSiチャネル部に加わる圧縮応力の影響に起因する. また、ゲート長の縮小に伴いμ<sub>n max</sub>の向上率が増大する ことも分かる. これはゲート長縮小による圧縮応力の 増加を示唆しており、Wangらの報告と一致している<sup>11)</sup>. 一方、V<sub>TH</sub>においてはゲート長が短くなるとV<sub>TH</sub>がプ ラス側にシフトしている. MOSFETの特性としてゲー ト長が短くなると短チャネル効果によりVTHが低下 (n-MOSFETの場合マイナス側へシフト, p-MOSFETの 場合プラス側へシフト)することが知られており、この 効果が観察されていると考えられる. また, x=0と0.3 の結果を比較するとGe濃度依存性で述べた圧縮応力に よるマイナスシフトが全てのゲート長で観察された.

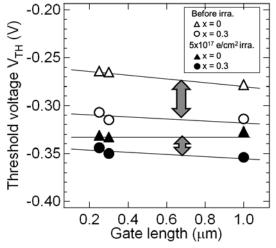

図 10. 電子線照射前の(a)最大正孔移動度と (b) 閾値電圧のゲート長依存性

図 11. 電子線照射前後の最大正孔移動度の ゲート長依存性(照射量: 5 x 10<sup>17</sup> e/cm²).

図12. 電子線照射前後の閾値電圧のゲート長依存性 (照射量: $5 \times 10^{17} \, \text{e/cm}^2$ ).

次に圧縮応力の強さを変動させるゲート長の違いが 電子線照射後のμ<sub>n max</sub>及びV<sub>TH</sub>の変動にどのような影響 を及ぼしたかを検証した. 前項で応力低下の傾向が見 られた $5 \times 10^{17} \, e/cm^2$  の電子線照射前後の各ゲート長で  $\mathcal{O}\mu_{n \text{ max}}$ と $V_{TH}$ を図11, 12に示す.  $\mu_{n \text{ max}}$ では, x=0のサ ンプルにおいては全てのゲート長でほぼ同程度の劣化 が観察されたのに対し、x=0.3のサンプルにおいては ゲート長が微細化するにつれてμ<sub>p max</sub>の劣化が大きく なる傾向が観察された. 即ち,強い圧縮応力が存在し ていたサンプルほど顕著な劣化が見られている.一方, V<sub>TH</sub>では,全てのゲート長において,ゲート酸化膜及び 酸化膜とSiチャネル部の界面の捕獲電荷の影響による V<sub>TH</sub> のマイナスシフトが観察され、 Ge濃度依存性の 結果と同様に、x=0と0.3との間の差異が照射後に減少 した. これらの結果からも電子線照射による応力低下 が示唆される.

#### 4. 結論

本研究では、歪 Si をチャネルに用いた MOSFET が、今後の高性能デバイスとして過酷な放射線環境下での用途に用いられることを想定し、その一例である  $Si_{1-x}Ge_x$  S/D p-MOSFET の電子線照射による電気的特性の劣化について評価を行った。評価は電子線加速器を用いて電子線を照射し、その前後の入力特性及び算出した最大正孔移動度と閾値電圧を比較することにより実施した。

圧縮応力を変化させる要素として Ge 濃度を変化させ、その依存性を検証したところ、SiGe ストレッサーに起因する圧縮応力による正孔移動度の向上効果は  $2 \times 10^{17} \ e/cm^2$ の照射までには保持されることが確認された. しかし、 $5 \times 10^{17} \ e/cm^2$ の照射においては、正孔移動度と Ge 濃度が有していた比例関係が崩れ、圧縮応力の低下を示唆する結果が得られた. 更に、 閾値電圧の変化においても、照射前に見られた Ge 添加による差異が減少していることから、歪 Si チャネル部の応力低下を示唆していると考えられる.

同じく圧縮応力を変化させる要素として,ゲート長を変化させた場合の依存性を検証したところ,正孔移動度とゲート長の依存性の結果より,5x10<sup>17</sup> e/cm<sup>2</sup>の照射後に圧縮応力の低下が示唆される結果が得られた.また,閾値電圧においても電子線による応力低下を示唆する結果が得られた.

今回、Ge濃度依存性及びゲート長依存性のいずれの結果からも、電子線照射による歪Siチャネル部の応力低下を示唆する結果が得られた。今後、歪Siチャネル部の応力低下をラマン分光測定法やTEM制限視野回折法を用いて直接測定し立証する予定である。

## 参考文献

- C. Claeys and E. Simoen: Radiation effects in advanced semiconductor materials and devices, Springer Verlag, New York, 2002.

- 2) ITRS 2009 Edition(JEITA 訳)pp.67-77.

- 3) M. Kodera, T. Iguchi, N. Tsuchiya, M. Tamura, S. Kakinuma, N. Naka and S. Kashiwagi: "Nanoscale Stress Field Evaluation with Shallow Trench Isolation Structure Assessed by Cathodoluminescence Spectroscopy, Raman Spectroscopy, and Finite Element Method Analyses", Jpn. J. Appl. Phys., Vol. 47, pp. 2506-2510, 2008.

- 4) M. B. Gonzalez, E. Simoen, N. Naka, Y. Okuno, G. Eneman, A. Hikavyy, P. Verheyen, R. Loo, C. Claeys, V. Machkaoutsan, P. Tomasini, S.G. Thomas, J.P. Lu, R. Wise: "Stress analysis of Si<sub>1-x</sub>Ge<sub>x</sub> embedded source/drain junctions", Mat. Sci. in Semi. Proc., Vol.11, pp. 285-290, 2008.

- 5) K. Rim, J. Welser, S. Takagi, J.L. Hoyt, and J.F. Gibbons: "Enhanced hole mobilities in surface-channel strained-Si p-MOSFETs", IEEE IEDM Tech. Dig., pp.517-520, 1995.

- C. K. Maiti, L. K. Bera, S. S. Dey, D. K. Nayak, and N. B. Chakrabarti: "Hole mobility enhancement in strained-Si p-MOSFETs under high vertical field", Solid-State Electronics, Vol.41, pp.1863-1869, 1997.

- 7) M. B. Gonzalez, E. Simoen, B. Vissouvanadin, N. Thomas, N. Taleb, P. Verheyen, A. Hikavyy, F. E. Leys, O. Richard, R. Loo, C. Claeys, V. Machkaoutsan, P. Tomasini, S.G. Thomas, J.P. Lu and R. Wise: "Impact of the Ge Content and the Epitaxial Thickness on the Bandgap Shrinkage Induced Leakage Current of Recessed Si<sub>1-x</sub>Ge<sub>x</sub> Source/Drain Junctions", SAFE Proc, pp. 496-500, 2007.

- 8) C. Claeys, E. Simoen, S. Put, G. Giusi and F. Crupi: "Impact strain engineering on gate stack quality and reliability", Solid State Electron., Vol.52, no.8, pp.1115-1126, 2008.

- P P. J. McWhorter and P. S. Winokur: "Simple technique for separating the effects of interface traps and trapped-oxide charge in metal-oxide-semiconductor transistors", Appl. Phys. Lett, Vol.48, pp.133-134, 1986.

- 10) T. Broiek, E. B. Lum and C. R. Viswanathan: "Oxide Thickness Dependence of Hole Trap Generation in MOS Structures under High-Field Electron Injection", Microelectron Eicngineering, Vol. 36, pp.161-164, 1997.

- C. C. Wang, W. Zhao, F. Liu, M. Chen, Y. Cao: "Modeling of layout-dependent stress effect in CMOS design", ICCAD proc, , 2009